Extras din curs

Schema bloc generală este dată în fig.5.1., unde:

În funcţie de tipul circuitului logic de pe calea de reacţie, automatele sincrone se clasifică după cum urmează:

- cu CBB de tip J-K pe calea de reacţie;

- cu CBB de tip D (registru de deplasare distribuit) pe calea de reacţie;

- cu numărătoare şi registre pe calea de reacţie;

- cu structuri complexe (ROM, RAM) pe reacţie.

5.1. Sinteza automatelor sincrone cu CBB de tip J-K pe calea de reacţie

Mai întâi se stabilesc nişte reguli privind utilizarea diagramelor K-V.

Se dă diagrama K-V din fig.5.2.a.

AB

CD

00

01

11

10

00 1 0 1 0

01 0 1 1 0

11 0 1 0 1

10 1 1 0 0

AB

C

00

01

11

10

0

D 1 0

1

1 0 D

Fig.5.2.a) Diagrama K-V b) Contracţia diagramei K-V

Prin contracţie diagrama K-V se reduce prin introducerea unei variabile în locaţiile diagramei eliminându-se 2 linii ale diagramei. Se obţine astfel o diagramă K-V cu variabile incluse.

Din tabelul din fig.5.3. se dau câteva reguli de contracţie:

Variabile

contractate Expresie ce se introduce în tabel V

x=0 x=1

m

n

p

q 0

0

1

1 0

1

0

1 0

x

1

I

II

III

IV

V 0

A

1

A

A A

0

A

1

B xA

A

+A

x+A

A+xB

a) b)

Fig.5.3.a) Tabelul cu reguli de contracţie; b) Deducerea regulilor pentru introducerea funcţiilor în diagrama K-V

Prin introducerea funcţiilor de una sau mai multe variabile în diagramele K-V se obţin reprezentări mai compacte, însă regulile de obţinere a formei minimale sunt complexe şi greu de aplicat.

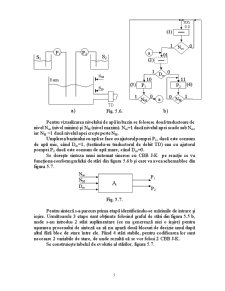

O metodă simplificată a regulii de minimizare cuprinde etapele:

1) În locaţiile cu “1” logic se consideră a fi valori indiferente şi se minimizează formând suprafeţe cu locaţii ce conţin aceeaşi funcţie (variabilă);

2) În locaţiile unde sunt incluse funcţii de una sau mai multe variabile se consideră ca fiind “0” logic şi se creează suprafeţe cu locaţii de “1” logic.

3) Se sumează logic produsele rezultate din cele două etape.

Exemplu: Se dă diagrama din fig.5.4.a.

Preview document

Conținut arhivă zip

- Sinteza Automatelor Sincrone.doc