Extras din proiect

CAPITOLUL I

CIRCUITE LOGICE SECVENTIALE (CLS)

Sistemele logice secventiale constituie o dezvoltare functionala a CLC,continand in plus elemente de memorie sau intarziere determinante a semnalelor,precum si unele bucle de reactie.

La aceste circuite,valorile functiei de iesire la un moment dat depind atat de valorile variabilelor de la intrare,cat si de starile elementelor de memorie,interne,ale circuitului(deci si de starea anterioara a circuitului)

CLS sunt larg utilizate pentru realizarea unitatilor de comanda si control,in automatizarea diferitelor procese.

CIRCUITE BASCULANTE BISTABILE(CBB)

Circuitele basculante bistabile reprezinta circuitele electronice care,din punct de vedere al parametrilor electrici,se caracterizeaza prin existenta a doua stari-limita,distincte.Trecere dintr-o stare in cealalta(bascularea circuitului)are loc intr-un timp in general scurt si apare ca o variatie brusca a marimilor electrice de la cele doua “iesiri” ale circuitului

Circuitele pot fi comandate prin impulsuri de comanda externe aplicate prin intrari.

Acest tip de circuit intalnit si sub denumirea de FLIP-FLOP,poate fi utilizat ca circuit de memorie,circuit de numarare,registru de deplasare,circuit de divizare a frecventei etc.

In functie de modul in care sunt comandate,CBB sunt de mai multe feluri,adecvate diverselor aplicatii in care sunt utilizate.

Cele mai uzuale sunt tipurile:

-bistabil R-S;

-bistabil J-K;

-bistabil D;

-bistabil T.

Treacera intr-o anumita stare poate fi determinate fie de semnalul care reprezinta informatia ce trebuie inscrisa in bistabil,fie de un semnal numit semnal de ceas(CLOCK) sau semnal de tact,notat in scheme CL,CK sau T.

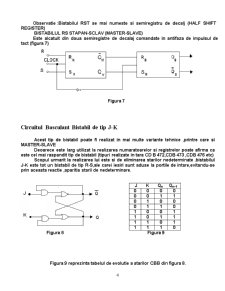

CIRCUITUL BASCULANT BISTABIL R-S

Comanda care permite aducerea CBB din starea de repaus(notata “0”) in starea de functionare (notata “1”) se noteaza cu S (SET-“punerea in pozitie

Comanda inversa,care aduce CBB in starea de repaus se noteaza prin R(RESET-“punere la zero”)

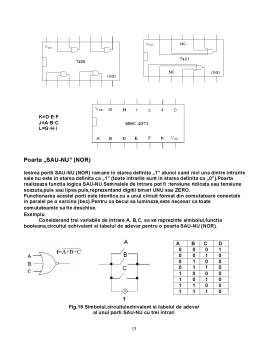

CBB de tip R-S in tehnica integrata poate fi compus fie:

-din doua circuite SAU-NU (NOR) Figura 1.

-din doua circuite SI-NU (NAND) Figura 2 cuplate intersectat.

Figura 1 Figura 2

Acest tip fundamental de CBB se mai numeste si LATCH (‘zavor ‘)simplu.

Aceasta denumire provine de la faptul ca in urma comenzilor externe,circuitul poate fi ‘zavorat ‘ in starea ‘sus’ cand Q=1 (inregistreaza bitul 1)sau ‘jos’ cand Q=0.

La analiza functionarii bistabilul R-S trebuie sa se tina seama de faptul ca,in momentul aplicarii semnalelor,CBB poate sa se afle in una dintre cele doua stari (stabile)deci trebuie se se ia in considerare toate combinatile posibile pentru iesirea activa Qn+1,in functie de starile existente in momentul aplicarii comenzilor.

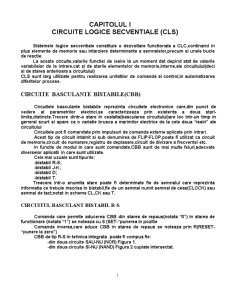

Operatiile logice pe care le poate efectua un bistabil R-S pot fi exprimate,in cazul din figura 1 prin urmatorul tabel de adevar :

R S Qn+1

0 0 Qn

0 1 1

1 0 0

1 1 ?

Qn+1-starea viitoare

Fig.3

Din tabelul de adevar pentru bistabilii cu porti NOR,rezulta urmatoarele concluzii :

a) Aplicarea semnalului „0” la ambele intrari nu modifica starea bistabilului ;

b)Aplicarea semnalului S=1,simultan cu R=0,determina Q=1,independent de setarea bistabilului,inainte de aplicarea comenzii.Aceasta trecere a bistabilului in starea Q=1 se numeste pozitionare (SET) ;

c)Aplicarea semnalului R=1,simultan cu S=0,determina Q=0,independent de starea anterioara a bistabilului.Aceasta operatie se numeste stergere (RESET)sau punere pe 0,pentru iesirea Q;

d)Aplicare simultana a semnalului 1 la intrarile S si R genereaza o stare nedeterminata ,de aceea comanda R=S=1 este interzisa (trebuie respectata conditia logica R•S=0)

In mod simultan se poate analiza un bistabil R-S,realizat cu porti NAND.Tabelul de evolutie a starilor va fi in acest caz urmatorul :

R S Qn+1

0 0 ?

0 1 1

1 0 0

1 1 Qn

Figura.4

Din tabel se vede de data aceasta starile interzise sunt R=S=0(aplicate simultan),ceea ce conduce la conditia

Circuitele bistabile R-S descrise sunt circuite asincrone.

Aceasta inseamna ca intrarile S si R sunt intrari de comenzi asincrone deoarece iesirea se modifica dupa ce se modifica oricare dintre intrari (prin aplicarea semnalelor)

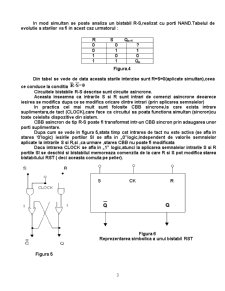

In practica cel mai mult sunt folosite CBB sincrone,la care exista intrare suplimentara,de tact (CLOCK),care face ca circuitul sa poata functiona simultan (sincron)cu toate celelalte dispozitive din sistem.

CBB asincron de tip R-S poate fi transformat intr-un CBB sincron prin adaugarea unor porti suplimentare.

Dupa cum se vede in figura 5,atata timp cat intrarea de tact nu este activa (se afla in starea ‘0’logic) iesirile portilor SI se afla in „0”logic,independent de valorile semnalelor aplicate la intrarile S si R,si ,ca urmare ,starea CBB nu poate fi modificata

Daca intrarea CLOCK se afla in „1” logic,atunci la aplicarea semnalelor intrarile S si R portile SI se deschid si bistabilul memoreaza comenzila de la care R si S pot modifica starea bistabilului RST ( deci aceasta comuta pe pelier).

Preview document

Conținut arhivă zip

- Circuit Basculant Bistabil.doc