Cuprins

- 1.Schema bloc a controlerului digital cu bistabile

- 2.Proiectarea secventiatorului

- 2.1 Diagrama stari si diagrama de timp

- 2.2 Tabela de succesiune a starilor

- 2.3 Proiectarea blocului secventiator

- 2.4 Schema blocului secventiator

- 3. Proiectarea blocului de comanda

- 4. Proiectarea blocului de vizualizare

- 4.1 LED- uri

- 4.2 Tranzistorul BC 547

- 4.3 Decodificatorul MMC4543

- 4.4 Afisorul KW1-1001AOA

- 5.Proiectarea generatorului de impulsuri cu frecventa variabila (GIFV)

- 6. Sursa de alimentare

- 7. Schema finala Detalii

- 8.Anexe

- 8.1 Circuitul MMC 4027 folosit pentru bistabilele J-K

- 8.2Circuitul integrat MMC 4093 folosit pentru blocul de comenzi start ,stop reset si init:

- 8.3 Circuit integrat MMC 4081 si 4071 pentru portile logice AND si OR

- Bibliografie

Extras din proiect

1.Schema bloc a controlerului digital cu bistabile

GIFV : generator de impulsuri de frecventa variabila; furnizeaza semnalul de tact pentru

controler cu o frecventa cuprinsa in plaja 0.5 – 10 Hz;

BC : bloc de comenzi; preia, memoreaza si prelucreaza comenzile operator: START, STOP,RESET,

INIT;

S : secventiator, generaza etapele care constituie ciclul functional;

D : driver; conduce impulsurile date de secventator spre blocul de vizualizare si sursa de

alimentare;

BV: bloc de vizualizare; contine led-uri si digiti pe 7 segmente;

EE : elemente de executie; comandate de controler;

SA : sursa de alimentare.

2.Proiectarea secventiatorului

Secventiatorul sau generatorul de etape este elementul central al proiectului. Acesta trebuie sa genereze secventa personalizata 07146 Secventiatorul este sintetizat cu bistabile J-K conectate intre ele prin porti logice dupa functiile deduse din secventa 07146.

2.1 Diagrama stari si diagrama de timp

Pentru un ciclu impus descris de secventa 07146 ( secventa scurta) diagrama de stari este prezentata in figura 1.

Fig.1

Pentru un impuls descris de secventa 301312515 (secventa lunga) diagrama de stari este prezentata in figura 2.

Fig.2

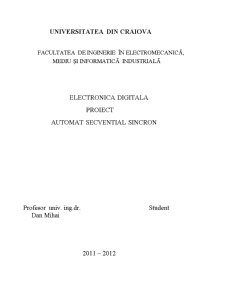

Pentru secventa scurta diagrama de timp este prezentata in figura 3.

Fig.3

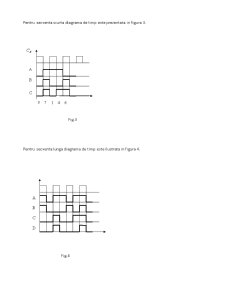

Pentru secventa lunga diagrama de timp este ilustrata in figura 4.

Fig.4

2.2 Tabela de succesiune a starilor

Tabela de adevar este ilustrata in tabelul 1.

J K Q(t) Q(t+1)

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 1 Toggle

1 1 1 0

Tabelul 1

Tabelul de intrari necesare pentru a obtine comutarile dorite este prezentat in tabelul 2.

Q(t) Q(t+1) J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

inital final intrari

Tabel 2

Tabela de succesiune a starilor pentru secventa 07146 este prezentata in tabelul 3.

Preview document

Conținut arhivă zip

- Electronica Digitala - Automat Secvential Sincron.doc