Extras din proiect

PARAMETRII CIRCUITELOR LOGICE INTEGRATE

CAPITOLUL I. NOTIUNI GENERALE

1.1 Introducere.Clsificare

O poarta este un circuit care indeplineste o functie logica.Principalii parametrii ai unei pozitii sunt:timpul (de intarziere la) propagare al informatiei logice de la intare catre iesire, tpd, puterea medie consumata de poarta, Pd si produsul primilor doi parametrii numit factor de calitate,Pq.Acest ultim parametru este un factor de merit al familiilor de circuite integrate digitale.

Tabelul 2.1 prezinta o situatie comparativa din punct de vedere al acestor trei parametrii pentru familiile de circuite logice existente.Circuitele logice ca baza de fabricatie siliciul si tehnologia planara a acestuia si se impart in principal in doua mari grupe:

circuitele bipolare , caracterizate prin frecventa mare de lucru si printr-o densitate a componentelor pe unitatea de suprafata a pastilei(capului)de siliciu mai mica;

GRUPA Familia

Timp de propagare

Tpd[ns] Putere consumata per poarta

Pd[mW] Factor de calitate

Pq[pJ] Frecventa maxima de lucru

Fmax[Mhz]

MOS PMOS(MOS canal P)

NMOS(MOScanal N)

CMOS/Si(MOS complementar)

CMOS/SOS(MOS pe safir) 50

20

30

3

1

1

~0,1

~0,1 50

20

3

<1 2

10

8

300

Fara echivalent cu componente discrete CCD

Memorii cu bule magnetice 50

1000

0,005

0,005 0,25

1 10

0,2

BIPOLARE TTL(standard)

HTTL(rapida)

LPTTL(de mica putere)

STTL(schottky,standard)

LPSTTL(schottky,de mica putere)

TSL(logica cu trei stari)

ECL(logica cuplata prin emitor)

I L(logica integrata de injectie) 10

6

35

3

10

3

<1

>10 10

22

1

20

2

22

50

<0,01 100

132

35

60

20

66

50

<1 35

50

3

120

35

70

1000

5

Neuron 0,2 10 10 0,2

Circuite unipolare (MOS) care au o densitate mai mare (cu 1÷2 ordine de marime) si sunt mai lente decat circuitele bipolare.In tabelul 2.1 se prezinta si circuitele logice care nu au echivalent in variante cu componente discrete.

In acest circuit se vor studia pe rand familiile de circuite logice ale caror principali parametri au fost prezenti in tabelul 2.1.

1.2 Circuitele se realizeaza in tehnologie bipolara

2.1 Principiul de functionare a portii TTL(Transistor Transisor Logic=Logica Tranzistor Tranzistor)

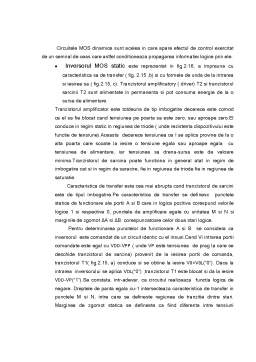

Poarta fundamentala cu ajutorul careia se poate genera orice functie logica este in aceasta familie poarta SI-NU(NAND), prezentata in varianta cu doua intrari In fig.2.1.Un circuit integral de tip CDB400 contine patru asemenea porti SI-NU cu cate doua intrari fiecare.Circuitul din fig.2.1.a) reprezinta o varianta evoluata si in forma integranta a portii DTL(Diode Transistor Logic=Logica Dioda-Transistor)care,din cauza unor dezavantaje specifice legate de viteza de operare , nu are perspective de dezvoltare.Functia logica este realizabila cu ajutorul tranzistorului multiemitor T1.Tranzistorul T2 indeplineste functia de comanda in contratimp (totem pole) a etajului de iesire realizat cu tranzistoarele T3 si T4 si cu dioda D.

Circuitele TTL dau fronturi mici( cateva manosecunde) din cauza carora pot aparea oscilatii parazite chiar daca firele de legatura intre porti sunt scurte.Oscilatiile apar deoarece aceste conexiuni se comporta ca linii de transmisie si sunt incarcate pe sarcini neadoptate.Astfel, de exemplu, frontul posterior (tranzactia’’s’’-‘’o’’ la iesire) al portii care comanda , poate genera salturi negative mai mari de 2V la intrarea portilor comandate.Daca celelalte intrari ale portii comandate se afla la +Vcc atunci jonctiunea emitor-baza corespunzatoare se poate stapunge atragand dupa sine un consum suplimentar de curent si generarea zgomotului.Ca remediu se folosesc diode de limitare pe intrari(D1,D2) care mai intai limiteaza saltul negativ al tensiunii(-0,7-1,5)V si apoi absorb suficienta energie din semnalul aplicat la intrare impiedicand aparitia supracresterilor pozitive ce vor putea reduce iesirea portii ce comanda la’’1’’.

Pentru a arata ca circuitul din fig.2.1, a) indeplineste functia logica SI-NU , sa presupunem mai intai ca toate intrarile se afla la un potential corespunzator valorii minime asoiate nivelului logic’’1’’ la intrare(2V).In aceste conditii jonctiunea EB ale tranzistorului de la intrare sunt polarizate invers si tranzistorul T1 lucreaza im regiunea active inversa.Tranzistorul T1 este proiectat sa aiba un B1<0,02.

Astfel , curentul de baza al tranzistorului T2 este asigurat in proportie de cel putin 98% de curentul prin R1 de la Vcc.In figura 2.1, a) se prezinta potentialele in puncte caracteristice ale circuitului in presupunerea simplificatoare ca tensiunea pe o jonctiune pn este polarizata direct este VBe=VD=0,7V.Circuitul este astfel proiectat ca atunci cand T1 conduce invers T2 sa fie saturat si, datoita tensiunii create de curentul sau emitor pe rezistenta R3, tranzistorul T3 sa inceapa sa conduca, urmand sa intre in saturatie datorita valorii corespunzatoare a curentului sau de baza. Se obtine astfel la iesirea circuitului tensiunea VceT3=0,2 V. Saturarea simultana a tranzistoarelor T3 si T4 trebuie evitata deoarece nivelele logice se alterneaza si circuitul se poate deteriora (la iesire sursei Vcc I se ofera o rezistenta de 130ᾨ+ rezistenta mica de iesire a tranzistorelor T3 si T4, de cateva zeci de ohmi fiecare).

Introducerea diodei D (un tranzistor legat ca dioda) impiedica intrarea in conductie a tranzistorului T4 si T3 este saturat deoarece potentialul punctului M nu este suficient pentru deschiderea tranzistorului T4 si a diodei D. Astfel, VM care este egal cu V CEsatT2+V Be satT3 este mai mic decat VBEe satT4+Vd + VcesatT3 cat ar fi nevoie daca T4 ar conduce la saturatie.S-a considerat ca VCEsat T2=VCEsatT3≈0,2V si VBEsat T3=VD=0,7V.

Rezulta, intr-adevar ca T4 este blocat cand T3 este saturat in cazul acestui montaj de iesire in contratimp format dintr-un repetor(T4) si un inversor(T3).

Asociind la intrare unei tensiuni mai mari ca 2V nivelul logic ‘’1’’ si unei tensiuni la iesire mai mici de 0,4V nivelul logic’’0’’, rezulta ca acest circuit asigura la iesire’’0’’ daca toate intrarile sunt la ‘’1’’.In figura 2.1,a) se dau curentii de intrare si de iesire corespunzatoarI.

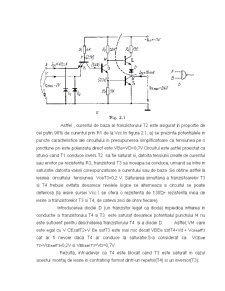

In figura2.2 sunt marcate tensiunile si curentii care rezulta cand cel putin una din intrari este la’’0’’ (corespunzator unei tensiuni de intrare mai mici de 0,8V) iar celelelte la ‘’1’’.Se va vedea sa in acest caz iesirea portii este la’’1’’(corespunzator unei tensiuni de iesire mai mari ca 2,4V), circuitul acesta verificand tabelul de adevar al functiei SI-NU.Potentialele prezentate in fig.2.2 sunt obtinute in presupunerea simplificatoare ca pe intrarea de nivel’’0’’ se afla 0V.

Preview document

Conținut arhivă zip

- Parametrii Circuitelor Logice Integrate.doc