Extras din laborator

Simularea structurilor hardware digitale cu ACTIVE-HDL

Această lucrare are ca principal obiectiv prezentarea mediului de

dezvoltare ALDEC ACTIVE HDL care va fi utilizat în cadrul acestui laborator

pentru implementarea de algoritmi în structuri hardware reconfigurabile cu ajutorul

limbajului de descriere hardware VHDL (Very high speed integrated circuit

Hardware Description Language). Vor fi realizaţi următorii paşi: realizarea unui

proiect, introducerea de programe in limbajul VHDL şi simularea acestora prin

vizualizarea semnalelor aferente.

Active-HDL este un mediu de dezvoltare integrat pentru limbajele de

descriere hardware VHDL, Verilog, VHDL-Verilog-EDIF, Sistem C şi Handle C.

El este compus din pachete integrate de proiectare, compilatoare pentru VHDL şi

Verilog, un singur kernel de simulare, pachete de programe pentru verificare,

pachete de programe pentru simulare cu vizualizare grafică sau în fişiere text. Mai

conţine utilitare pentru gestionarea resurselor proiectelor, librăriilor predefinite şi

posibilitatea de conectare software cu alte pachete de programe în procesele de

sinteză şi implementare hardware a programelor realizate de utilizator

Laborator 1 UNIVERSITATEA PITEŞTI

În plus, Active-HDL include un mediu de simulare pentru VHDL şi

Verilog în vederea determinării funcţionării fiecărui modul în cadrul unui proiect.

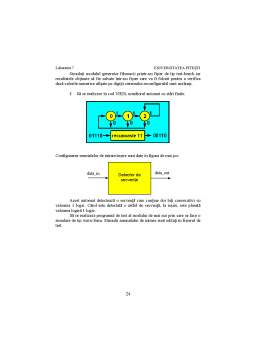

Învăţarea utilizării mediului de dezvoltare Active-HDL se va face prin

implementarea unui modul digital descris în această lucrare şi va fi încadrat în

schema electrică din figura de mai jos:

Se doreşte implementarea unui program în structura programabilă de

tip FPGA a unui program VHDL astfel încât la fiecare apăsare a tastei SW1 se

va aprinde pe rând câte un led începând cu LED0 şi până la LED7. Apăsarea tastei

TEST/RESET (se găseşte în partea stângă jos a machetei) conduce la stingerea

tuturor ledurilor.

Schema electrică din figura anterioară este o mică parte din schema

machetei de laborator cu SPARTA 3. În această schemă sunt plasate numai

componentele utilizate în cadrul proiectului pe care dorim sa-l realizăm. În circuitul

FPGA va fi implementat programul descris în continuare şi care respectă enunţul

problemei.

Programul VHDL este realizat ierarhic pe trei module:

- modulul COUNTER, care realizează numerotarea apăsărilor succesive a

tastei SW1;

- modulul DECODER, care realizează conversia unui număr binar pe 4

digiţi, primit pe portul de intrare în formatul ONE HOT pe 8 biţi care

este plasat pe ieşire la LED-uri dând efectul de deplasare a unui led

aprins de la LED0 la LED7;

- al treilea modul, numit TOP, face legătura între primele două module şi

formează structura finală ce urmează a fi implementată în FPGA.

Porturile modulului COUNTER sunt: clk, reset şi Q[3..0]

Porturile modulului DECODER sunt: DataIn[3..0] şi Output[7..0]

Porturile modulului principal sunt: clk, reset şi Output[7..0]

Preview document

Conținut arhivă zip

- lab1_VHDL.pdf

- Lab10_VHDL.pdf

- Lab2_VHDL.pdf

- Lab3_VHDL.pdf

- Lab4_VHDL.pdf

- Lab5_VHDL.pdf

- Lab6_VHDL.pdf

- Lab7_VHDL.pdf

- Lab8_VHDL.pdf

- Lab9_VHDL.pdf