Extras din proiect

Microprocesorul AM2901

AM 2901 este un circuit ALU, un processor bit-slice reaelizat in tehnologie bipolara si organizat pe 4 biti.

Schema bloc a circuitului este urmatoarea:

aceasta este schema arhitecturala a procesorului.

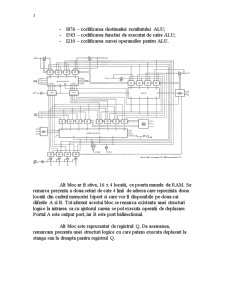

Schema functionabila a circuitului este urmatoarea:

Un prim bloc ar fi decodificatorul de microinstructiuni orientate pe trei campuri distincte in functie de semnificatia bitilor respective:

- I876 – codificarea destimatiei rezultatului ALU;

- I543 – codificarea functiei de executat de catre ALU;

- I210 – codificarea sursei operanzilor pentru ALU.

Alt bloc ar fi stiva, 16 x 4 locatii, ce poarta numele de RAM. Se remarca prezenta a doua seturi de cate 4 linii de adresa care reprezinta doua locatii din cadrul memoriei biport si care vor fi disponibile pe doua cai diferite A si B. Tot aferent acestui bloc se remarca existenta unei structuri logice la intrarea sa cu ajutorul careia se pot executa operatii de deplasare. Portul A este output port, iar B este port bidirectional.

Alt bloc este reprezentat de registrul Q. De asemenea, remarcam prezenta unei structuri logice cu care putem executa deplasari la stanga sau la dreapta pentru registrul Q.

ALU = Unitate Aritmetico-Logica de viteza. Ea poate executa 8 operatii dintre care 3 aritmetice (o adunare A+B si doua scaderi A-B si B-A) si 5 logice.

Codificarea operanzilor:

ALU: - port A de RAM

- port B de RAM

- registru Q

- external data input

- logic 0

Codificarea destinatiei rezultatului ALU:

- daca sa incarce outport-ul ALU ( cu sau fara shiftare ) in memoria RAM

- daca sa incarce outport-ul ALU ( cu sau fara shiftare ) sau continutul registrului Q ( cu shiftare ) in registrul Q

- daca outport-ul ALU sau continutul portului A sa fie trimis la portul extern de date.

PORTURI

INPUT SI OUTPUT PORTURI:

Preview document

Conținut arhivă zip

- Proiectarea Sistemelor Logic Programabile - Microprocesorul AM2901

- Aplicatii

- alu.v

- core.v

- core_test.v

- dec_dest.v

- dec_sursa.v

- dpram.v

- mux_2_1.v

- mux_2_1_out.v

- mux_3_1.v

- qshifter.v

- regq.v

- shifter.v

- test1.v

- test_alu.v

- test_mux_3_1.v

- test_shifter.v

- Documentatie

- Proiectarea Sistemelor Logic Programabile - Microprocesorul AM2901.doc