Extras din proiect

BISTABIL DE TIP D.

Dezavantajul principal al latch-urilor de tip RS constă în aceea că pentru valori identice ale intrărilor (R=S=1) apar tranziţii nedeterminate inclusiv pentru cele comandate cu impulsuri de tact. Pentru a elimina acest dezavantaj se apelează la structuri de tip D (latch simplu) figura 1.a.; în figura 1.b se arată reprezentarea simbolică.

Figura 1 Structura bistabilului de tip D

În majoritatea aplicaţiilor practice CBB mai sunt înzestrate cu încă două intrări de comandă PRESET şi respectiv CLEAR (RESET) pentru punerea directă a CBB în poziţia SET şi respectiv ştergerea (CLEAR) a acestuia înainte (sau în afara) aplicării semnalelor CLK şi D. Aceste semnale se utilizează când nu se aplica tactul (CLK=0) deci sunt intrări asincrone, de tip prioritar, ele fiind folosite la începutul funcţionării schemei, când trebuie resetat ansamblu de bistabili (CLEAR) sau puşi într-o anumită stare de iniţializare conform cerinţelor problemei date (PRESET). Cele două intrări mai sunt notate cu Sd (PRESET) şi Rd(RESET).

Nedeterminarea R=S=1 este înlăturată prin legarea împreună a intrărilor R şi S printr-un inversor astfel încât întotdeauna când S=1 avem simultan R=0.

Tabelul de stări al bistabilului D este:

Dt Qt Qt+1

0 0 0

0 1 0

1 0 0

1 1 1

Din tabelul de adevăr şi din schema logică a CBB de tip D se vede că la ieşirea Qt+1 se

obţine întotdeauna starea aplicată intrării D în acord cu ecuaţiile logice de funcţionare a

bistabilului D:

Qt+1=Dt

Q ̅_(t+1)=D ̅_t

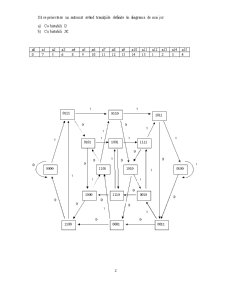

Astfel bistabilul D apare ca un repetor dar el realizează şi principala funcţie a CBB şi

anume aceea de întârziere cu un tact a datelor de la intrare, de unde şi denumirea bistabilului D (delay - întârziere). După cum se vede din diagramele de timp din figura 2 bistabilul D urmăreşte la fiecare impuls de tact evoluţia intrării simţind la ieşire modificarea intrării de date pe toată durata palierului activ al ceasului. Ieşirea este modificată la apariţia fiecărui impuls de tact (când devine activ 1) adică pe frontul anterior al impulsului de tact (punctele 1,2, 3 din diagramele de timp) şi se menţine zăvorât în starea în care se găseşte în momentul când impulsul de tact devine inactiv (CLK=0); pe durata când CLK=0 ieşirea bistabilului nu este modificată indiferent de ce se aplică la intrarea de date D, deoarece pentru CLK=0 porţile ŞI de la intrare sunt închise.

CLK

D

Q

Figura 2. Semnale de intrare şi ieşire corespunzătoare bistabilului de tip D

Preview document

Conținut arhivă zip

- Analiza si Sinteza Cicuitelor Numerice.docx