Cuprins

- 1. Se bazează pe ideea că decodificatorul poate fi şi el validat.Arhitecturi de SMP în variantă distribuită 1

- Principii structurale (topologice) 1

- Un procesor poate avea 2 realizări fizice: 2

- Principii de comunicaţie între 2 procesoare 5

- Partajarea memoriei în SMP 6

- Arhitecturi SMP utilizând procesoare monoplacă 7

- Arhitecturi obţinute prin comparaţia C1,C2, C3 adăugând şi memorii concentrate de tip M3 7

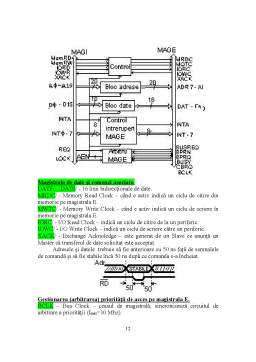

- Magistrale standard pentru SMP 10

- Magistrala de date şi comenzi asociate. 12

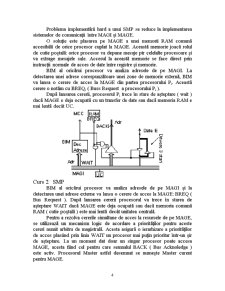

- Gestionarea (arbitrarea) priorităţii de acces pe magistrala E. 12

- Întreruperi de magistrală 13

- Liniile de alimentare 13

- Linii de protecţie la căderea alimentării. 13

- Caracteristicile electrice ale magistralei MULTIBUS. 14

- Magistrala SMS AMS 14

- Blocul de întreruperi pe MB 16

- Întreruperile nevectorizate de magistrală 16

- Întreruperile vectorizate de magistrală 17

- Considerente esenţiale SOFTWARE privind SMP 18

- Excluziunea 18

- Comunicaţia. 19

- Sincronizarea 19

- Principii de partajare a memoriei comune în SMP cu module procesor monoplacă 19

- Conceptul de memorie dublu acces (dublu port) 19

- Conceptul de memorii dublu port 19

- Memoria accesibilă doar pe MAGI (sistem cu 2 mag.) 19

- Sistem cu memorie RAM dublu port 20

- Avantajele structurii 21

- Logica de control 22

- Unitatea operaţională UO 24

- Convenţie privind sensul de circulaţie al informaţiei prin buffer-e 24

- Gestiunea serială. 25

- Gestiunea paralelă. 26

- Tehnici şi structuri de implementare a arbitrării 27.

- Tehnici de alocare a priorităţii. ` 28

- Structuri de arbitrare. 29

- Structura FPLS. 30

- Criteriul autonomiei funcţionale 30.

- Modul Slave pentru ax 31

- Rejecţia perturbaţiilor de mod comun 32

- Mărirea rezoluţiei de măsură. 32

- Partea logică de referinţă. 32

- Determinarea Offset axe. 33

- Unitate duală de prelucrare a datelor 33

- Circuitul capacităţilor de configurare variabilă 34

- Alte registre multiprocesor. 35

- Magistrale importante. 35

- Magistrala VME. 36

- Specificaţii electrice şi mecanice ale mag VME. 36.

- Protocolul transmisiei informaţiei. 37

- Arbitrarea pe VME. 38

- Funcţii speciale pe VME. 39

- Magistrala P896 . 40

- Specificaţiile fizice şi electrice pentru magistrala P896. 40

- Module Slave 42

- 1. Organizarea unui MS. 42

- a)utilizând comparatoare 44

- b) Porţi logice 44

- c) Cu decodificatoare. 45

- d) Decodificare paralelă. 45

- e) Decodificare utilizând memorii PROM 46

- CUPRINS 47

Extras din curs

Curs 1

Introducere

Abordarea structurală a sistemelor de proiectare pentru procese complexe cum sunt comanda numerică cu calculatorul (CNC) a maşinilor unelte şi a echipamentelor de comandă a roboţilor industriali conduce la configuraţii de tip multiprocesor. Acestea permit automatizări flexibile locale spre exemplu în sisteme flexibile de fabricaţie. Sistemul multiprocesor (SMP) reprezintă soluţii ale unor probleme complexe de automatizări în timp real acolo unde e necesar un timp de răspuns rapid (perioadă de şantionare ns sau μs), şi un mare necesar de calcul.

În SMP o funcţie de bază este comunicarea între μsistemele componente realizată prin mesaje precum şi sincronizarea execuţiei programului de aplicaţie. Conceptele fundamentale referitoare la arhitectura şi modul de proiectare al SMP sunt descrise de două str de bază:

• Structuri multiprocesor cu module funcţionale distribuite

• Structuri multiprocesor cu module funcţionale concentrate

Arhitecturi de SMP în variantă distribuită

Principii structurale (topologice)

Eficienţa unui SMP e legată în principal de eficienţa cu care se efectuează schimburile de informaţii între modurile (procesoarele) SMP. Prin procesor se înţelege un sistem cu μprosesor ce include unitatea de calcul şi resursele periferice. Modurile de conectare a procesoarelor pentru a realiza schimbul de informaţii în SMP pot fi grupate în patru categorii:

a) Stea. Oferă simplitate, liniaritate şi o bună toleranţă la defectare. Dacă un procesor se defectează, acesta poate fi izolat sistemul fiind capabil să lucreze în continuare prin preluarea în mod dinamic a sarcinilor procesorului defect. Această arhitectură este utilizată intensiv în conducerea proceselor industriale datorită avantajelor mai sus menţionate.

b) Inel. Se caracterizează prin posibilitatea comunicării directe numai cu 2 vecini. Comunicaţia cu un procesor mai îndepărtat se face prin intermediul procesoarelor de pe calea care asigură legătura între aceste două procesoare.

Avantaj: dpdv hardware, structura interfeţelor cu cei doi vecini este identică indiferent de numărul procesoarelor din SMP.

Dezavantaj: la defectarea unui procesor sau a unei magistrale banda de comunicaţii este întreruptă ea putând fi realizată pe o altă cale mai lungă.

c) Matriceală. Prezintă simplitate faţă de soluţia b). (interfaţa cu MAGE este simplă: o singură legătură).

Dezavantaj: comutatorul (partea logică) care dirijează cuplarea mag în nodurile reţelei este complexă dpdv hard şi la defectarea lui SMP nu mai funcţionează.

d) Magistrala complet conectată. Se caracterizează printr-o înaltă siguranţă în funcţionare dar este costisitoare sub raportul conexiunilor, al interfeţelor şi al prg de comunicaţie.

Un procesor poate avea 2 realizări fizice:

a) un ansamblu de module standard: UC, memorii, periferice; bloc de interfaţă cu magistrala SMP (BIM). Toate aceste module sunt conectate în jurul unei magistrale interne (MAGI).

b) un procesor este realizat dintr-un μcalculator pe o singură placă (Single Board Computer – SBC) care include pe o singură placă toate modulele funcţionale din fig.2.

Structura SMP stea a) se reduce la MAGE la care se conectează prin BIM-uri module procesor Pi ; i=1,n.

Numărul de procesoare P poate fi extins până la limita de încărcare nominală a MAGE. O soluţie pentru a extinde MAGE constă în plasarea pe anumite procesoare a unuia sau mai multe canale de comunicaţie serială. Acestea fac posibilă conectarea la un alt procesor plasat pe o altă MAGE (aparţinând altui SMP) o structură de SMP expandabilă constituită din mai multe structuri stea care comunică prin linii seriale.

Preview document

Conținut arhivă zip

- Sisteme Multiprocesor.doc